A D-PHY Configuration always includes:

- One Clock Lane, and

- One or more Data Lanes

All Data Lanes must support:

- High-Speed transmission in the Forward Direction

- Escape Mode in the Forward Direction

All lanes may optionally support Alternate Low-Power (ALP) mode.

Types of Data Lanes

There are two main types of Data Lanes:

| Data Lane Type | Directionality | Reverse Communication Support |

|---|---|---|

| Bi-directional | Forward & Reverse | Supports Turnaround and reverse signaling |

| Unidirectional | Forward only | No reverse signaling |

Reverse Communication Options (for Bi-Directional Lanes)

Bi-directional Data Lanes may support one or both of:

- High-Speed Reverse communication

- Low-Power Reverse Escape Mode (with or without LPDT)

Escape Mode and ALP Mode Support

- Escape Mode must be supported in the Forward Direction for:

- ULPS (Ultra-Low Power State)

- Triggers

- Additional Escape Mode or ALP mode features are optional and can be specified per application.

- For Bi-directional Lanes, Escape Mode and ALP behavior may be configured independently in each direction.

Configuration Flexibility

A PHY Configuration offers the following degrees of freedom:

- Number of Data Lanes (single or multiple)

- For each Data Lane: Unidirectional or Bi-directional

- For each Bi-directional Lane: supported reverse communication type(s)

- Escape Mode functionality (per direction per lane)

- ALP mode functionality (per direction per lane)

- Data encoding:

- 8-bit raw data (default), or

- 8b/9b encoded symbols (optional)

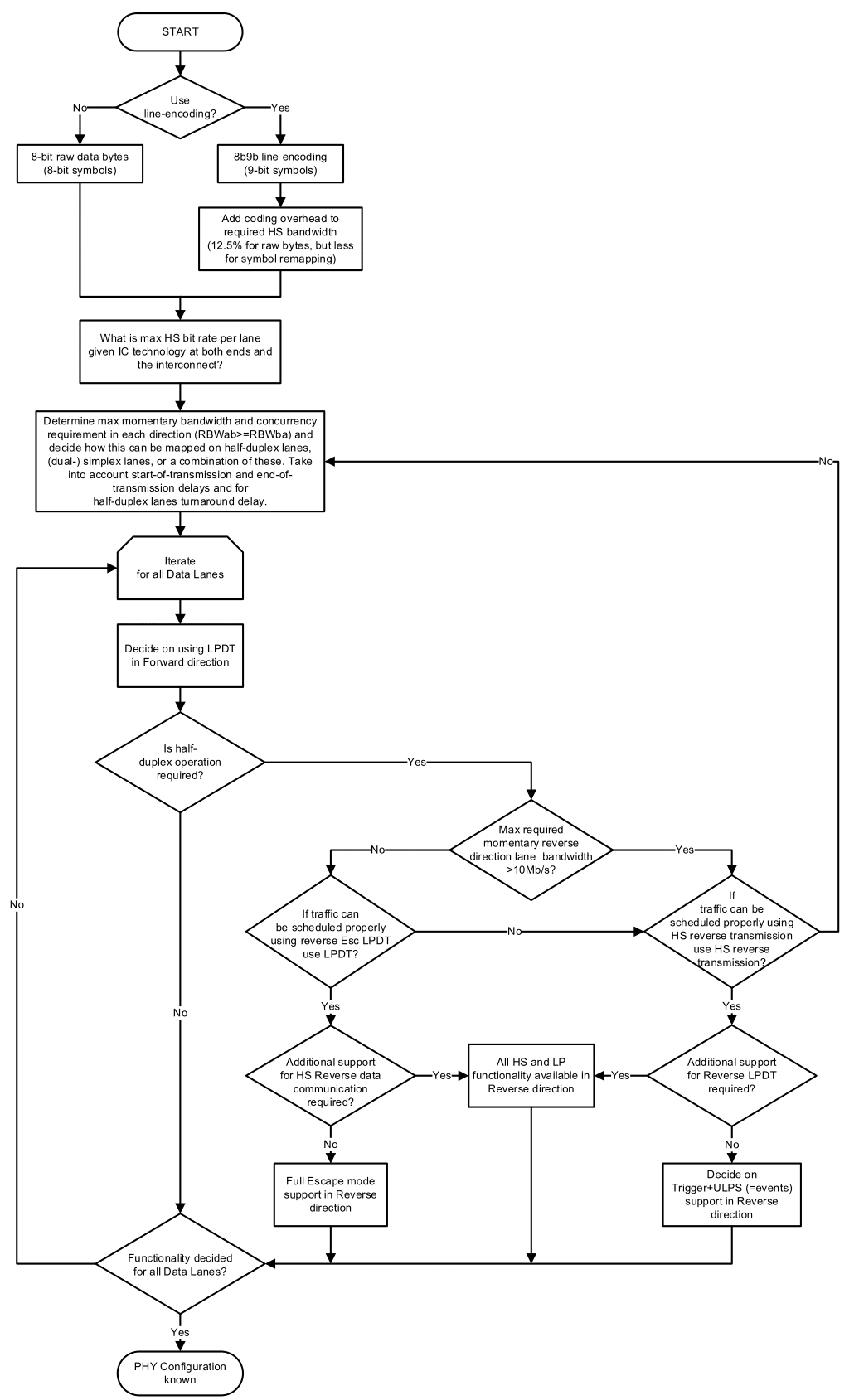

Flow Diagram